VLSI Lab 4 Verilog MegaWizard IP Generator (Compiled on Quartus II v20.1) - 2024 simplified version

VLSI Lab 4, EIE, 2024 version

Laboratory Objectives

The objectives of this laboratory are:

· Understand the use of Altera’s MegaWizard IP generator: (https://ftp.intel.com/Public/Pub/fpgaup/pub/Teaching_Materials/current/Tutorials/Verilog/Using_Library_Modules.pdf)

· How to specify synthesis options and their impact

· Understand the impact of placement on the design quality using Pin Planner

Project files are archieved in Google drive:

Top entry sqrt.v file:

// ----- EIE Lab 4

// ----- https://vlsiorfpgadesign.blogspot.com/ ----- //

// Using IP core altsyncram

module sqrt (

sqrt_in,

sqrt_out);

parameter width = 4; // # bits

input [width-1:0] sqrt_in;

output [width:0] sqrt_out;

wire [width/2-1:0] q_sig; // quotient

wire [width/2:0] remainder_sig; // rmainder

sqrt_ip U1_sqrt_inst (

.radical(sqrt_in),

.q(q_sig),

.remainder(remainder_sig));

assign sqrt_out = {q_sig[width/2-1:0], remainder_sig[width/2:0]};

endmodule

// -------------------------------------- //

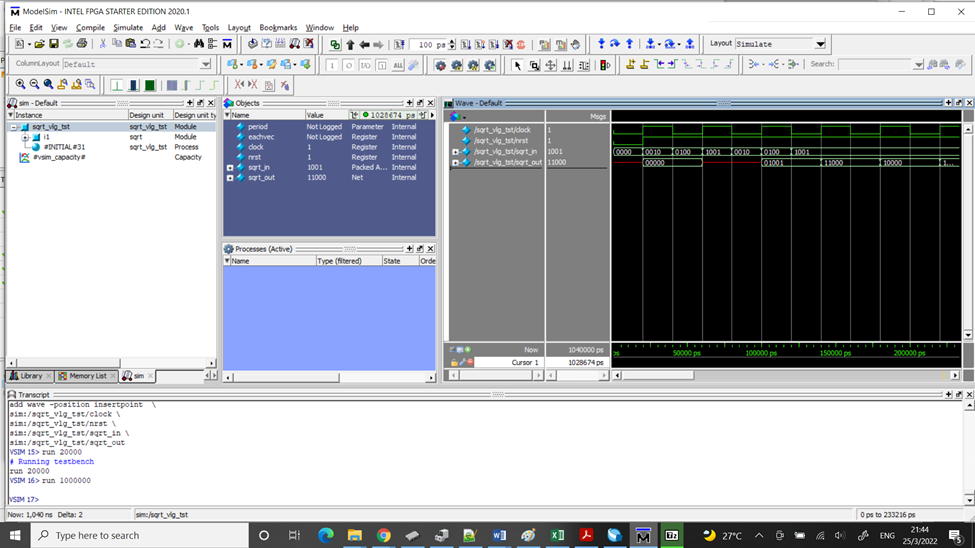

Simulation results:

Thank for sharing blog read more Best ai tools in 2025

回覆刪除