VLSI Lab 3

This article is to present a Verilog code for Sequence Detector using Moore FSM. A Verilog Testbench for the Moore FSM sequence detector is also provided for simulation below.

Lab learning objectives:

• Learn to create FSM in Verilog

• Use File IO in testbench

• User the debugger to display internal signals

• Synthesis options using

o GUI

o Synthesis directives

The Moore FSM keeps detecting a binary sequence from a digital input and the output of the FSM goes high only when a "1011" sequence is detected. For a state diagram of the Moore FSM for the sequence detector, you might refer to the website at this hyperlink: https://www.fpga4student.com/2017/09/verilog-code-for-moore-fsm-sequence-detector.html

You can also find some similar verilog files of the lab are placed in the Google Drive (hyperlink below), for reference: (you can just download the Quartus files)

https://drive.google.com/drive/folders/1ARnWCZSUym3DMnA0rp0RT7bdNTfso2CN?usp=sharing

Design Architecture:

State Diagram (Click the picture to enlarge)

Verilog code is designed as an example as follows:

// ----- https://vlsiorfpgadesign.blogspot.com/ ----- //

// ----- ** SeqDetect.v ** Start Here ** ----- ----- //

// EIE511 FPGA projects, Verilog projects

// Verilog project: Verilog code for Sequence Detector using Moore FSM

// The sequence being detected is "10110" or One Zero One One

module SeqDetect(seq_in,clock,reset,seq_out

);

input clock; // clock signal

input reset; // reset input

input seq_in; // binary input

output reg seq_out; // output of the sequence detector

parameter SIZE = 3,

IDLE=0, // "IDLE" State

S1=1, // "S1" State

S2=2, // "S2" State

S3=3, // "S3" State

S4=4; // "S4" State

reg [(SIZE-1):0] current_state, next_state; // current state and next state

// sequential memory of the Moore FSM

always @(posedge clock, posedge reset)

begin

if(reset==1)

current_state <= IDLE; // when reset=1, reset the state of the FSM to "IDLE" State

else

current_state <= next_state; // otherwise, next state

end

// combinational logic of the Moore FSM

// to determine next state

always @(current_state,seq_in)

begin

case(current_state)

IDLE:begin

if(seq_in==1)

next_state = S1; // 1

else

next_state = IDLE; // 0

end

S1:begin

if(seq_in==0)

next_state = S2; // 10

else

next_state = S1; // 11

end

S2:begin

if(seq_in==0)

next_state = IDLE; // 100

else

next_state = S3; // 101

end

S3:begin

if(seq_in==0)

next_state = S2; // 1010 or 10

else

next_state = S4; // 1011 input detected

end

S4:begin

if(seq_in==0)

next_state = IDLE; // 1011 0

else

next_state = S1; // 1011 1

end

default:next_state = IDLE;

endcase

end

// combinational logic to determine the output

// of the Moore FSM, output only depends on current state

always @(current_state)

begin

case(current_state)

IDLE: seq_out = 0;

S1: seq_out = 0;

S2: seq_out = 0;

S3: seq_out = 0;

S4: seq_out = 1;

default: seq_out = 0;

endcase

end

endmodule

// ----- ** SeqDetect.v ** Ends Here ** ----- ----- //

// ----- ----- ----- ----- ----- ----- ----- ----- //

// -------------------------------------------------------------------- //

A Verilog Testbench for the above Moore FSM Sequence Detector:

// ----- https://vlsiorfpgadesign.blogspot.com/ ----- //

// ----- ** tb_SeqDetect.v ** Start Here ** ----- ----- //

// EIE511 FPGA projects, Verilog projects ----- //

// Verilog project: Verilog code for Sequence Detector using Moore FSM

// The sequence being detected is "1011" or One Zero One One

`timescale 1ns / 1ps

module tb_SeqDetect();

// Inputs

reg seq_in;

reg clock;

reg reset;

// Outputs

wire seq_out;

// Instantiate the Sequence Detector using Moore FSM

SeqDetect uut (

.seq_in(seq_in),

.clock(clock),

.reset(reset),

.seq_out(seq_out)

);

initial begin

clock = 0;

forever #5 clock = ~clock;

end

initial begin

// Initialize Inputs

seq_in = 0;

reset = 1;

// Wait 100 ns for global reset to finish

#30;

reset = 0;

#40;

seq_in = 1;

#10;

seq_in = 0;

#10;

seq_in = 1;

#20;

seq_in = 0;

#20;

seq_in = 1;

#20;

seq_in = 0;

// Add stimulus here

end

endmodule

// ----- ** tb_SeqDetect.v ** Ends Here ** ----- ----- //

// ----- ----- ----- ----- ----- ----- ----- ----- //

There are different ways to encode the states of the FSM. There are different synthesis options when using the Altera's GUI (dialog windows): e.g. sequential, one-hot, or Gray code. Synthesis directives can also be applied (instructed directly in the Verilog source codes)

(a) Using Altera GUI’s synthesis directives:

Select Assignments > Settings > Compiler Settings >

Advanced Settings (Synthesis) (button) > State Machine Processing

The synthesis result (report) can be found at: "Analysis & Synthesis" > "View Report"

----- ----- ----- ----- -----

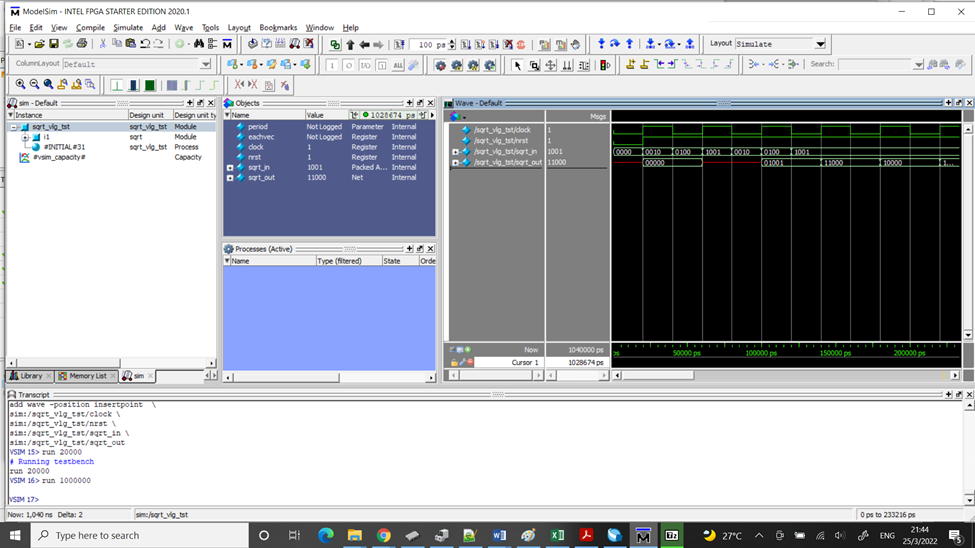

Below is the RTL simulation waveform using Altera-Modelsim (Quartus II v20.1): (Click it to enlarge)

With the sequence input "1011", the current state of the FSM changes at the rising edge of "clock" signal, from the state "IDLE" to "S1" and changes as the sequence: IDLE > S1 > S2 > S3 > S4 > S2.

(Click the picture to enlarge)

// --------------------------------------------------------------------------------------------- //

// --------------------------------------------------------------------------------------------- //

Extend the work to detect the sequence "10110":

One more state is added below.

Verilog Design File: SeqDetect.v (To detect the sequence “10110”)

// ----- https://vlsiorfpgadesign.blogspot.com/ (SeqDetect.v)

* Starts Here ----- //

// The sequence being detected is "10110"

or One Zero One One Zero ----- //

module SeqDetect(seq_in,clock,reset,seq_out

);

input clock; // clock signal

input reset; // reset input

input seq_in; // binary input

output reg seq_out; // output of the sequence

detector

parameter

SIZE = 3,

IDLE=0, //

"IDLE" State

S1=1, //

"S1" State

S2=2, //

"S2" State

S3=3, //

"S3" State

S4=4, //

"S4" State

S5=5; //

"S5" State

reg [(SIZE-1):0] current_state, next_state; //

current state and next state

// sequential memory of the Moore FSM

always @(posedge clock, posedge reset)

begin

if(reset==1)

current_state <= IDLE;// when reset=1, reset the state of the FSM to

"IDLE" State

else

current_state <= next_state; // otherwise, next state

end

// combinational logic of the Moore FSM

// to determine next state

always @(current_state,seq_in)

begin

case(current_state)

IDLE:begin

if(seq_in==1)

next_state

= S1; // 1

else

next_state

= IDLE;

end

S1:begin

if(seq_in==0)

next_state

= S2; // 10

else

next_state

= S1;

end

S2:begin

if(seq_in==0)

next_state

= IDLE;

else

next_state

= S3; // 101

end

S3:begin

if(seq_in==0)

next_state

= S2; // 10

else

next_state

= S4; // 1011

end

S4:begin

if(seq_in==0)

next_state

= S5; // 10110

else

next_state

= S1; // 10111 >

end

S5:begin

if(seq_in==0)

next_state

= IDLE; // 101100

else

next_state

= S3; // 101101 > S3

end

default:next_state = IDLE;

endcase

end

// combinational logic to determine the output

// of the Moore FSM, output only depends on current state

always @(current_state)

begin

case(current_state)

IDLE: seq_out = 0;

S1: seq_out = 0;

S2: seq_out = 0;

S3: seq_out = 0;

S4: seq_out = 0;

S5: seq_out = 1;

default: seq_out = 0;

endcase

end

endmodule

// ----- ** SeqDetect.v (10110) ** Ends Here ** ----- ----- //

// ----- ----- ----- ----- ----- ----- ----- ----- //

// --------------------------------------------------------------------------------------------- //

ModelSim Results:

There are different ways to encode the FSM

states. To modify the FSM encoding scheme from (i) sequential (ii) one-hot and(iii) Gray, we can (a) using Altera’s

GUI synthesis options dialog window or (b) using the synthesis

directives (directly at the source code) (a) Altera GUI’s synthesis directives: (a) Select Assignments à Settings à Compiler Settings

à

Advanced Settings

(Synthesis) <button>

à State Machine Processing

Synthesis with Different Settings: (for Sequence Detector "10110")

1) One-Hot:

(Click to enlarge)

2) Minimal Bits:

(Click to enlarge)

3) Johnson

留言

張貼留言